カリフォルニア大学リバーサイド校(UCR)のチームは、シリコンでできた微小な“部品”の形やつなぎ方を細かく調整し、電子をあえて“波”として扱うことで電流の流れ方そのものを切り替える手法を示した。水面の波がぶつかって高く盛り上がったり、反対に打ち消し合って静かになるのと同じで、電子の波も重ね方しだいで強くも弱くもなる。この性質を利用し、わざと打ち消し合い(破壊的干渉)を起こす配置では電気が流れにくくなり、逆に波同士のタイミング(位相)を合わせて重ねる配置では流れやすくなる。いわば、分子サイズの“オン・オフ”スイッチをシリコンの中に作り込んだわけである。

成果は Journal of the American Chemical Society に報告され、UCRの発表でも取り上げられた。特筆すべきは、極低温に冷やさなくても働く見通しが示された点である。液体ヘリウムで冷却するような大がかりな装置を前提にせず、室温近くで波の重ね合わせを制御できるなら、実用化までのハードルは一段低くなる。実現のカギは微細加工にあり、光刻やエッチングでナノスケールの配線や結合の取り回しを作り分け、電子の通り道とその“足並み”を設計する。これにより、分子スイッチや量子干渉型トランジスタ、低電力ロジックといった応用が視野に入る。しかも材料がシリコンであるため、既存の半導体製造プロセスや設計資産をそのまま活かしやすい。要するに、理論的な面白さにとどまらず、工場で量産する現実へ橋を架ける一歩になったと言える。

ニュース詳細

シリコン分子の対称性で電流をオン・オフ

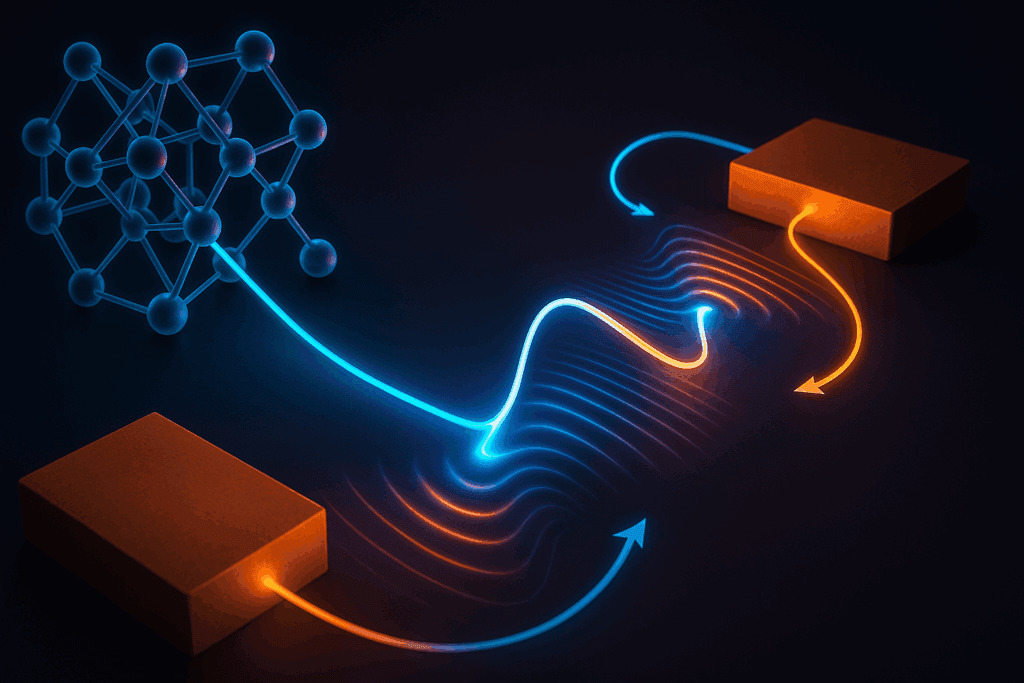

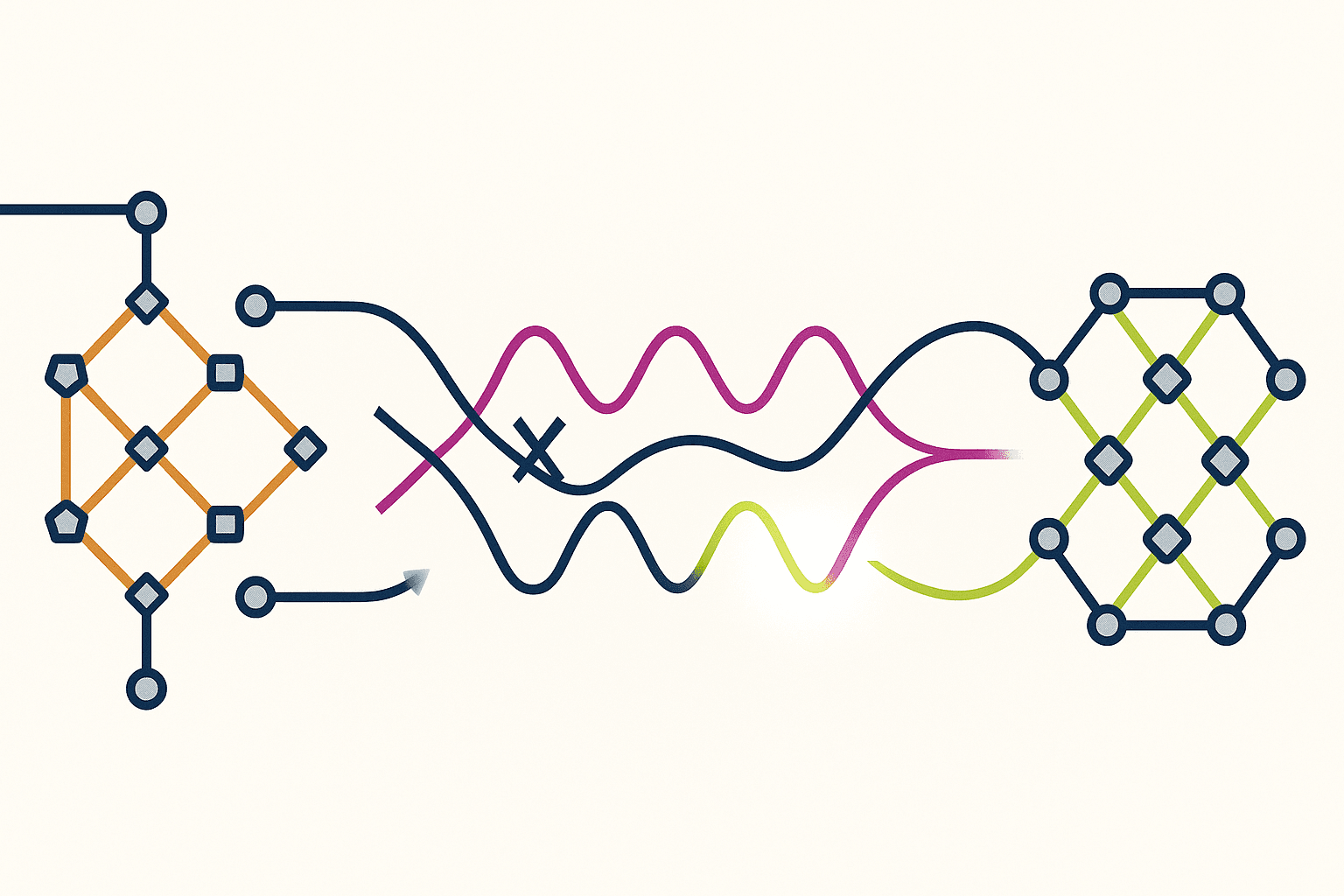

UCRのTim Suらは、シリコンが本来もつダイヤモンド格子の“骨組み”をまねた分子パターンを使い、そのつなぎ目や結合角、電極への当て方を細かく作り分けた。狙いは、電子を粒ではなく波として扱い、分子の中で進める“抜け道”を複数用意することにある。波は重ね方しだいで強くも弱くもなるため、あえてタイミングが逆になる経路を一つ混ぜると互いに打ち消し合い、電気の流れ(実効コンダクタンス)が目に見えて落ちる。逆に、波の山と山、谷と谷がそろうように道筋を整えれば、重なりが強まり電流は通りやすくなる。こうして分子の形そのものを“位相調整つまみ”に見立て、オンとオフを切り替える仕組みを作ったわけだ。しかもこの動作が室温近くで成り立つことを示した点が肝で、極低温に頼らずに分子スイッチとして使える可能性を一気に高めたと言える。

ナノファブで“経路”と“位相”を設計する

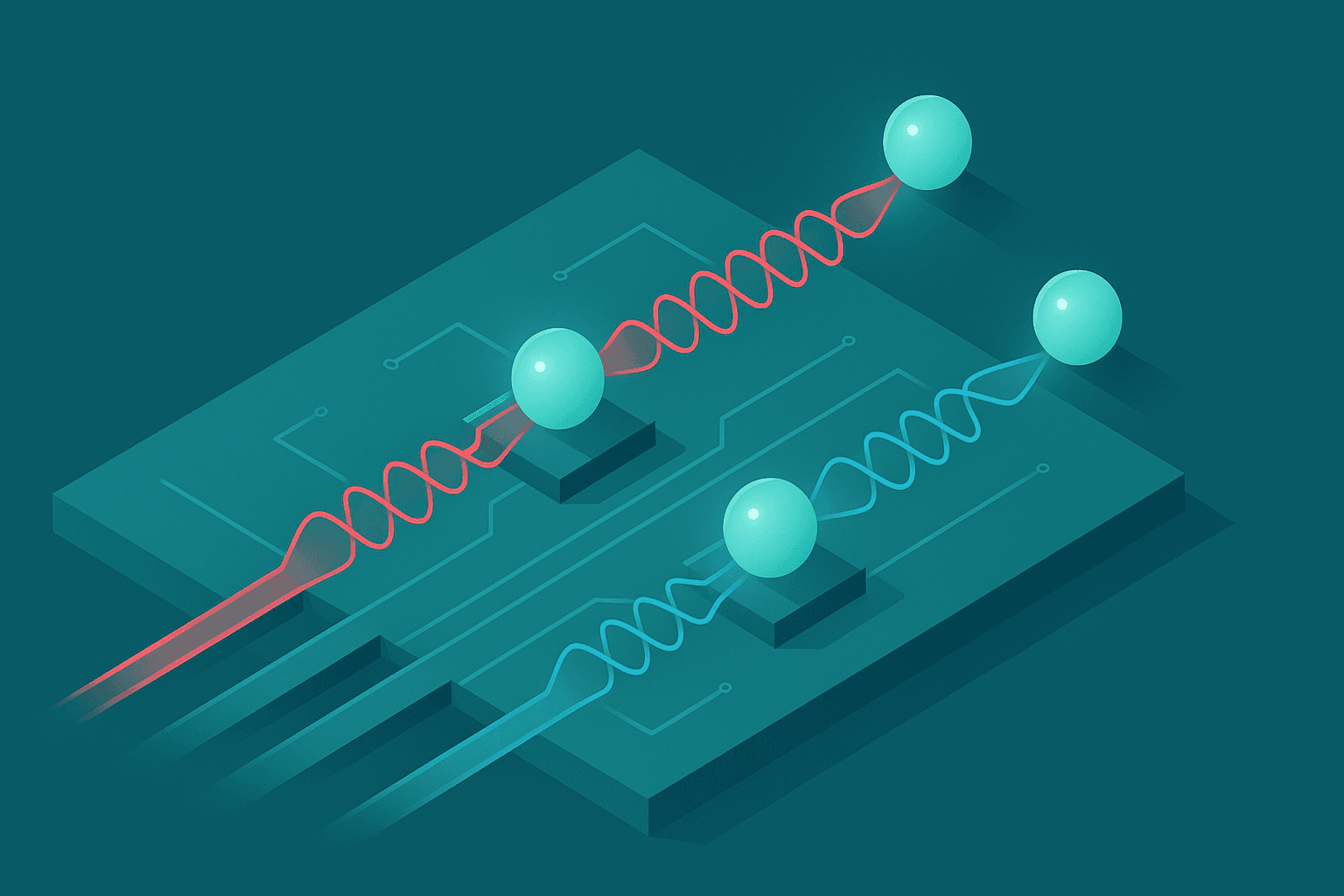

研究チームは、電子線で極細のパターンを描き、不要な部分を原子レベルで削るドライエッチングを組み合わせることで、分子ワイヤーの内部にある“橋”や“回り道”を意図的に作り分けた。分子の中に複数の通り道ができると、そこを進む電子の波はそれぞれ違うタイミングで到着し、重なり方が変わる。どの結合を経由させるかを選ぶこと自体が、波の山と谷の位置――すなわち位相――を調整する操作になり、結果として強め合いが起きる配置では電流が通りやすく、打ち消し合いが強く出る配置では電流が極端に細くなる。

測定では、この“重なり方の違い”が導電性にそのまま現れ、特定の置換や配列を選ぶと電気の流れが桁違いに落ち込む現象が繰り返し観測された。干渉の模様が導電度のグラフに縞のように刻まれることから、研究者はこれを干渉縞、さらに構造ごとに固有の落ち込みパターンを干渉指紋と呼ぶ。重要なのは、こうしたオン・オフの変化が不純物の濃度(ドーピング)や障壁の高さを微調整して得られたものではなく、分子内の“道のつなぎ方”というトポロジーそのものを設計変数として扱うことで生まれている点である。言い換えれば、材料の性質を外から押し込むのではなく、通り道の組み合わせと位相の合わせ方で電気の流れを支配しているのであり、この発想が分子スケールの省電力スイッチ設計に新しい自由度を与える。

産業材料“シリコン”を使う実利

量子干渉デバイスといえば有機π共役分子の実験例が目立ってきたが、土台をシリコンに置き換える利点は圧倒的に大きい。まず、シリコンはCMOSの標準材料であり、光刻からドライエッチング、成膜、平坦化、配線まで量産の道具立てが一式そろっている。つまり、今回のような分子スケールの“位相で配線する”素子を作っても、既存ラインの温度予算や材料互換性に合わせて工程へ組み込みやすい。電源・クロック配線、熱拡散、エレクトロマイグレーション耐性といった周辺の設計知見もそのまま流用でき、測定やテスト手順も既存のプローブ技術に乗せやすい。結果として、研究室のプロトタイプで終わらず、歩留まりと信頼性を確保しながら段階的にスケールアップする道筋が最初から見えている点が大きいのである。

さらに、CMOSと同一基板上でのハイブリッド集積が現実味を帯びる。従来のFETで論理やメモリの骨組みを担わせつつ、リークを極小化したい部分や比較器・センスアンプのように閾値が重要なブロックに干渉スイッチを差し込む構成が考えられる。干渉由来のオン・オフは電荷の大移動を伴わないため、動作電圧を下げやすく、発熱源にもなりにくい。配線抵抗や寄生容量が支配的になる先端ノードでは、この特性が電力密度の抑制に直結する。加えて、シリコンはパッケージングや実装のエコシステムが厚く、TSVやチップレット技術による三次元実装とも折り合いがよい。要するに、この成果は“面白い現象を見せた”にとどまらず、量産の現実へと渡るための互換性という橋を最初から備えている点に産業的価値がある。これが有機π系中心の流れに対して、シリコン系干渉デバイスが持つ決定的なアドバンテージである。

応用ロードマップと残る技術課題

応用範囲は、分子レベルでオン・オフできるスイッチから、干渉効果で動作点を決める新型トランジスタ、待機時の電流漏れを極小化したロジック回路、微小な信号を拾う量子計測デバイスまで連なっている。たとえば比較器やセンスアンプのように閾値の鋭さが命の回路では、干渉で電流経路そのものを細く太くできれば感度と省電力を同時に稼げる。メモリ周辺ではリークが支配的になりやすいが、電荷を大きく移動させず位相で切り替える方式なら、待機電力の抑制に直結する。計測分野では、干渉に由来する導電度の落ち込みを“指紋”として使い、分子の結合状態や外場のわずかな変化を読み解くセンサーが狙える。いずれも室温近くで動く見通しがある点が重要で、冷却コストを強いられない設計自由度が確保される。

同時に、越えるべきハードルは明確である。電子の波の足並みを乱す欠陥や不純物、格子振動に起因するフォノン散乱をどこまで抑え込めるかが第一の壁だ。分子スケールでは原子一つの欠けや配置のズレが位相に効き、再現性を損なう要因になるため、プロセスの微小ばらつきを設計で吸収する工夫が欠かせない。第二に、個々の素子で得られた干渉効果を、チップ全体に広げても破綻しないようにするスケーラビリティの検証が要る。配線抵抗や寄生容量、熱の逃げ道といったマクロな制約が、ミクロの位相制御と干渉しないレイアウト指針が必要になる。これらの最適化と量産プロセスでの歩留まり確保にメドが立てば、電荷の大移動ではなく“位相で配線する”という考え方が、室温・低電力・高集積という三条件を同時に満たす現実的な回路として立ち上がってくる。言い換えれば、材料を替えるのではなく、通り道の結び方と波の合わせ方を回路資源に昇華できるかが、次の勝負どころである。

専門家解説

ポイント整理

量子シリコン制御の肝は三点に集約できるが、要は“波としての電子を設計で操る”という一点に尽きる。まず第一に、電子は粒ではなく波でもあるという事実を前提に、分子のつなぎ方=トポロジーを道具として使う。波同士の重ね合わせが合うように道筋を設計すれば電流は通り、あえてずらせば互いに打ち消し合って細くなる。つまり、電圧やドーピングで無理に押すのではなく、“位相で配線する”発想でオン・オフを作るのである。第二に、シリコン分子の対称性や結合の取り回しを整えることで、室温でも干渉がはっきり現れる条件を引き出せた点が大きい。極低温に頼らず、普段使いの環境で波の足並みを揃えられるなら、実装までの距離はぐっと縮まる。第三に、材料が最初からシリコンであるため、光刻やエッチング、配線・放熱といった半導体プロセスの蓄積をそのまま活かせる。研究室の面白い現象に終わらず、量産ラインへ橋渡ししやすい土台が用意されているわけだ。これら三つがかみ合うことで、低電力・小型・高集積という相反しがちな要件を同時に満たす現実解に近づく。

さらに解説

この研究の核心は、電流のオン・オフを“量子干渉”そのもので作り出す点にある。従来のようにトンネル障壁の高さを少しずついじったり、ドーピング量を加減したりする力業に頼らず、分子ワイヤーの中にどんな“橋”や“回り道”を設けるかという配線の組み方で勝負している。電子は波として複数経路を同時に進むため、道のつなぎ方しだいで波の山と山、谷と谷が合うか外れるかが決まり、合わなければ互いに打ち消し合って伝導チャネルが痩せる。発想はダブルスリット実験と同じだが、舞台がシリコンのσ結合ネットワークという実材料系であることが新しく、結合角や接続位置を選ぶだけで位相関係を細かく設計できる自由度が手に入った。実際、JACSに示されたデータでは特定の置換や接続パターンで伝導が桁単位で落ち込む“干渉指紋”がはっきり現れ、どの構造が強い破壊的干渉を生むかが地図のように読み解ける。これはデバイス設計にとって実用的な指針であり、低電圧で確実にオフれるスイッチや、リークの少ないロジックを狙う際の最短ルートを与える。言い換えれば、材料の性質を外側から押し曲げるのではなく、分子内部の“道の編み方”と“位相の合わせ方”で電気の流れを根本から制御するやり方が、シリコンという量産素材の上で具体的な設計論として立ち上がったのである。

キーワード解説

- 量子シリコン制御:シリコン分子やナノ構造の幾何を設計し、電子波の位相を操作して伝導を制御する概念である。破壊的干渉で電流を抑え、建設的干渉で流す“分子スイッチ”を室温で狙う。 UCRニュース

- 量子干渉:複数経路を進む電子波が重なり、強め合い/打ち消し合いを起こす現象である。干渉条件は経路長や結合トポロジーに依存し、分子配線の設計指標となる。 ACS Publications

- 破壊的干渉:位相が反転した波同士が重なって伝導が下がる状態である。シリコン分子では結合経路の選別で意図的に引き起こせることが示された。 ACS Publications

- シリコン分子(ダイヤモンド構造モチーフ):バルクSiのユニットセルと同型のクラスターやオリゴシランを指す。電極の当て方で干渉様式が変わる特性を持つ。 ACS Publications

- 分子スイッチ:分子レベルの構造変化や位相制御でオン・オフを作る素子である。干渉駆動型はリーク低減と低電圧動作が期待される。 SciTechDaily

- JACS論文(2025):sila-adamantane等でσ軌道の破壊的干渉を実証した研究。分子配線の橋渡し経路を削る“ブリッジカット”で干渉の起源を特定した。DOI:10.1021/jacs.5c04272。 ACS Publications

まとめ

量子シリコン制御の価値は、誰もが使い慣れたシリコンという土台の上で、“波の足並み=位相を配線する”という発想を現実の設計に落とし込みつつある点にある。電子を粒ではなく波として扱い、分子の中に用意した通り道の組み合わせで重なり方を操れば、電流は自然に強まったり弱まったりする。しかも極低温の冷凍機に頼らず室温でこの効果を引き出せる見通しが立てば、手のひらサイズの装置や既存プロセスでも扱いやすい。分子スケールのスイッチや、干渉でオン・オフを決めるトランジスタが、低電力かつ小型という条件を満たしたまま量産の議論に乗る可能性が高まるわけだ。

もちろん、越えるべき課題ははっきりしている。位相を乱す微小な欠陥や不純物、熱ゆらぎに伴う雑音をどこまで抑え込めるかが第一の関門であり、素子ごとのバラつきを許容範囲に収めながら大規模に並べる集積化の設計も避けて通れない。とはいえ、材料がシリコンである以上、既存の半導体プロセスやパッケージ技術を活かす余地は大きい。次の一歩は、試作レベルで得られた干渉の“指紋”を回路ブロックへ確実に組み込み、室温・低電力・高集積を同時に達成できるかどうかである。当サイトの量子デバイス特集では、この路線の追跡を継続する。ブックマークしておけば、設計指針の更新や実証の節目を逃さずキャッチできるはずだ。

参考文献

- 元記事 URL: Quantum Zeitgeist | University of California, Riverside, Demonstrates Quantum Silicon Control Quantum Zeitgeist

- 参考:UCR公式ニュース(2025年7月8日)「Scientists find new way to control electricity at tiniest scale」 UCRニュース

- 参考:Journal of the American Chemical Society(2025)“Quantum Interference in a Molecular Analog of the Crystalline Silicon Unit Cell” DOI:10.1021/jacs.5c04272 ACS Publications

- 参考:Phys.org 紹介記事(2025年7月) Phys.org