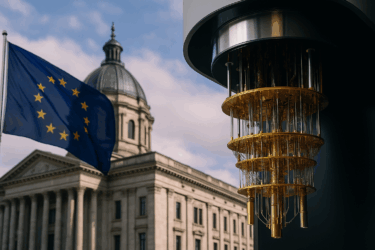

富士通は2025年8月1日、自社が培ってきた超伝導技術を土台に1万量子ビットという巨大規模の量子コンピューターを作ると正式に宣言した。目標時期は2030年度で、この装置では物理ビットを束ねて信頼性を高めた論理量子ビットを250個確保し、計算の心臓部には独自開発のSTARアーキテクチャを据える。STARは位相回転ゲートを巧みに使うことで誤り訂正に必要なビット数を抑えられる設計で、将来的に6万ビット級へ拡張しても従来のスーパーコンピューターを上回る速度が見込める点が強みだ。このプロジェクトはNEDOの「ポスト5G基盤強化事業」に採択され、産総研や理研と組んで2027年度まで共同研究を進める。鍵となるのは、ジョセフソン接合をナノメートル単位で均一に作り込む製造技術、複数チップを極低温で無理なく配線するパッケージング技術、そして熱負荷を抑えた制御回路の高密度実装である。富士通は完成後も開発を止めず、ダイヤモンドスピン量子ビットと組み合わせるハイブリッド方式に踏み込み、2035年度には1,000論理量子ビットへ到達するロードマップを描いている。

ニュース詳細

10,000量子ビットの壁を越える設計思想

富士通が目指す1万量子ビット量子コンピューターは、例えるなら都市規模の発電所を一つの小さなチップ上に収めるようなものだ。量子ビットが増えるほど誤りの混入リスクは雪だるま式に膨らむが、同社のSTARアーキテクチャはその弱点を最小限に抑える仕組みを持つ。位相回転ゲートという部品を効率良く並べ替えることで、同じ回路面積でもより多くの論理量子ビットを確保でき、ハードウェアの負担を大きく軽減できるからだ。こうして実現する250論理量子ビットは、分子の電子軌道を原子レベルで追跡するシミュレーションや、数十万種類の化合物を一気にスクリーニングする材料探索を短時間でこなす計算能力をもたらす。新薬候補の反応経路を秒単位で予測したり、高性能電池の正極材料を瞬時にふるいにかけたりといった、従来のスーパーコンピューターでは数週間かかっていた処理が日常的に行えるようになる可能性が高い。

NEDOプロジェクトと産学連携の意味

NEDOの国家プロジェクトに採択されたことで、研究費という燃料だけでなく、国内最高峰の知識と設備が一つに束ねられる体制が整った。超微細加工を専門とする産総研は、ジョセフソン接合を原子数レベルの誤差で作り分ける技術を担い、量子ビット間のばらつきを最小限に抑える役割を果たす。理化学研究所は、64ビット機から256ビット機へと段階的に大型化させてきた実績を背景に、極低温冷凍機と制御電子回路を隙間なく統合するノウハウを提供する。富士通は、この二つの成果を自社の量子制御ICと「FUJITSU-MONAKA」プロセッサ群に接続し、従来のスーパーコンピューターが得意とする高性能計算と量子計算を同じシステム基盤の上で協調動作させるプラットフォームを構築する計画である。これにより、古典計算機が担当する前処理や後解析と、量子コンピューターが担う膨大な組み合わせ探索を一気通貫で回せる計算環境が生まれ、材料開発や創薬など産業応用の実証が飛躍的に進む見通しだ。

スケーリングを阻む3つの技術課題

最初の難関は「高スループット製造」である。量子ビットの心臓部を形づくるジョセフソン接合は、一つでも周波数がずれると誤り訂正全体の足を引っぱるため、数万個を一気に作っても特性がほぼ揃う超精密ラインが欠かせない。歩留まりが下がれば論理量子ビットの数を稼げず、実機性能が机上の計算に追いつかなくなる。次の壁は「チップ間接続」だ。1万ビット級ともなれば単一ダイに収まりきらず、複数チップを極低温で縫い合わせる必要があるが、配線が長くなるほど信号遅延と熱流入が増え、量子状態は途端に脆くなる。極低温下でメートル単位の信号経路をミクロン精度で配列する技術が求められる。最後に立ちはだかるのが「低コスト制御回路」で、現在の方式では1ビットにつき一本の同軸線が必要になり、1万本規模のケーブル束が冷凍機へ熱を持ち込んでしまう。富士通は制御ICを量子チップの近くまで冷やし込むCryo-CMOS技術を導入し、さらに誤り訂正デコーダをハードウェア化して演算主体を冷凍槽の外へ追い出すことで、配線本数と熱負荷の同時削減を図る方針を示している。

専門家解説

ポイント整理

量子情報学の立場から見ると、このプロジェクトの真髄は「早期フォールトトレラント」、すなわち完全な百万ビット級を待たずに誤り訂正の効きを体感できる段階をいち早く証明するところにある。誤りを自動で修復できる250論理量子ビットが手に入れば、分子の結合状態を原子単位で解析する化学シミュレーションや、データの特徴量を量子空間に写し取って精度を高める量子カーネル法といった用途で、既存のスーパーコンピューターを実時間で上回る計算速度が期待できる。しかも、誤り訂正を使わず過渡的な性能を狙うNISQ時代とは異なり、アルゴリズムが安定して動くため、企業の生産ラインや研究開発ワークフローにそのまま組み込みやすいという実務上の利点が大きい。

さらに解説

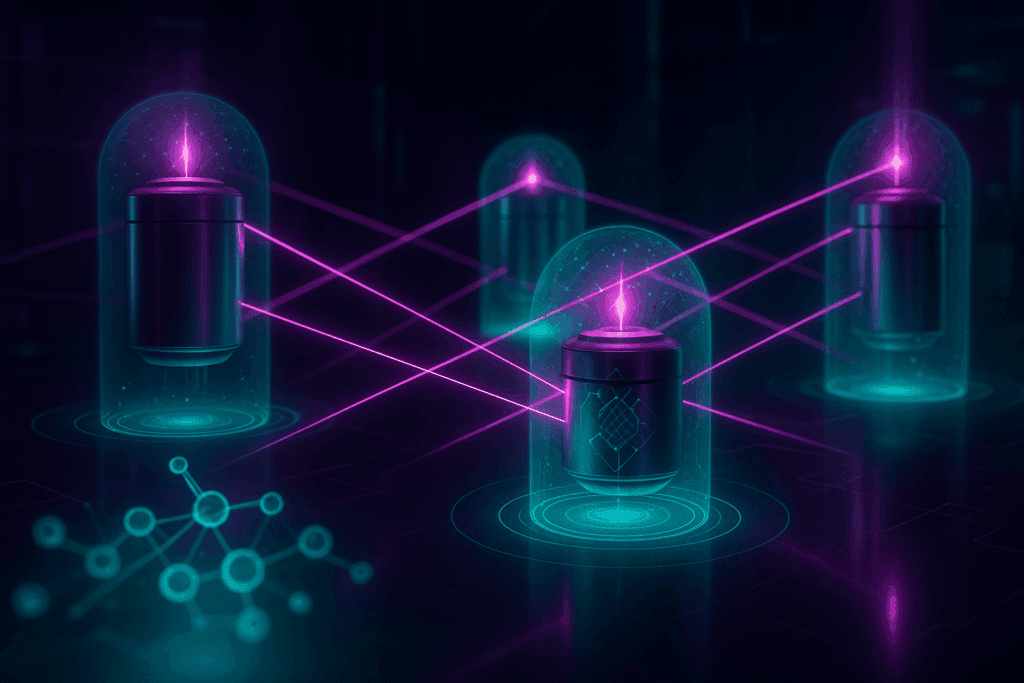

量子ビットは外部ノイズに非常に敏感で、たとえ一瞬の振動や温度揺らぎでも簡単に計算結果が崩れてしまう。そこで研究者は、壊れやすい物理量子ビットを何十個も束ねて「一塊の頑丈な論理量子ビット」として扱う誤り訂正の仕組みを用いる。一般的には一つの論理量子ビットを守るのに三十〜五十個もの物理量子ビットが必要とされるが、富士通はSTARアーキテクチャを採用することで二十個前後まで減らせる見通しを示している。これは同じチップ面積でより多くの計算ユニットを詰め込めることを意味し、言い換えれば「狭い校庭で人数分の机を並べる工夫」をしたようなものだ。さらに富士通は機械学習向けに回路を最適化し、アルゴリズムの種類に合わせて物理ビット配置を微調整することで、誤り訂正に費やすリソースをいっそう圧縮しようとしている。一方、チップ同士をつなぐ低温配線は冷凍機に熱を持ち込みやすく、大規模化の足かせになってきた。これに対し、ダイヤモンドスピン量子ビットを光で結合する方式は、光ファイバーで離れたサーバーをリンクさせるように、複数の冷凍機に分散した量子チップをフォトン経由で接続できる潜在力を持つ。もし光子による相互接続が実用化されれば、各冷凍機が一つの演算ノードとなり、それらを束ねて構築した巨大クラスタが事実上の量子スパコンとして機能する未来像が開けるだろう。

キーワード解説

- 1万量子ビット量子コンピューター:富士通が2030年度に稼働を狙う超伝導式巨大マシン。実効250論理量子ビットで、医薬品や電池材料の分子モデルを短時間で解ける産業向け計算基盤となる。

- STARアーキテクチャ:位相回転ゲートを効率的に組み込み、物理量子ビットの浪費を抑えつつ誤り訂正を実装できる富士通独自回路設計。early-FTQCの鍵を握る。

- 論理量子ビット:多数の物理量子ビットを束ね、エラー自動修復機構で守られた高信頼ビット。実際の演算はすべてこの単位で行われるため、数が性能を左右する。

- NEDO:新エネルギー・産業技術総合開発機構。国費を投じて量子を含む先端技術を産業化へ導く日本の中核ファンドで、今回の大型計画にも資金と監督を提供。

- ジョセフソン接合:二枚の超伝導体を絶縁膜で挟んだ微小トンネル素子。周波数が揃わないと量子ビット全体が乱れるため、大量生産精度が大規模化のボトルネックになる。

- 誤り訂正デコーダ:量子測定結果に潜むエラー位置を高速推定し、適切な補正信号を返す頭脳役。専用ハードウェアで並列処理しないと論理ビットが増えるほど計算が追いつかない。

まとめ

1万量子ビット量子コンピューターの完成は、日本の量子研究が教科書の中の理論ではなく、実際のビジネスを動かす「道具」に進化したと世界に示す試金石になる。このマシンが動けば、薬の候補化合物を瞬時にふるいにかけたり、次世代電池の材料を丸ごとシミュレーションしたりと、従来のスーパーコンピューターでは膨大な時間を要した作業が日常業務の一部としてこなせるようになる。もっとも、1万量子ビットを絶対零度近くで安定稼働させるには、冷凍機の熱管理や配線の密度、誤り訂正の計算量といった技術障壁が高くそびえている。その突破口を開くのが、ハードウェア負荷を軽くするSTARアーキテクチャと、産総研・理研をはじめとする研究機関との濃密な連携である。基礎科学の知見と民間企業の製造ノウハウを一気通貫で結びつけることで、極低温かつ超大規模という二重のハードルを乗り越え、世界市場で通用する「使える量子計算」を実現する最短ルートが描かれつつある。当サイトでは、開発の節目や産業応用の成功例を逃さず追跡し、量子技術特集で随時レポートを更新していく。急速に動く最前線を見失わないよう、ブックマークして最新動向をともに追ってほしい。

参考文献

- 元記事:https://global.fujitsu/en-global/newsroom/gl/2025/08/01-01

- Fujitsu STARアーキテクチャ解説論文:https://arxiv.org/abs/2408.01234

- NEDOポスト5G事業概要:https://www.nedo.go.jp/activities/ZZJP_100171.html